Начался предзаказ средств разработки на новой платформе UltraScale

Уважаемые коллеги!

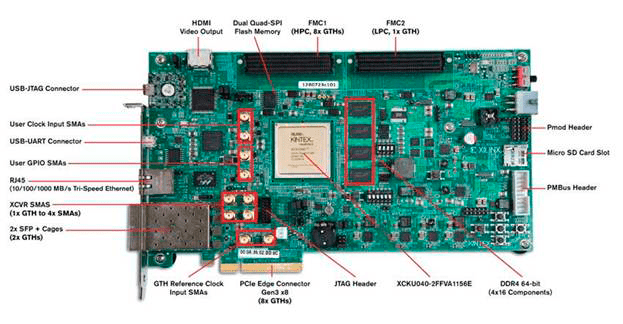

Начался предзаказ средств разработки на новой платформе UltraScalе – KCU105.

Основные характеристики:

-

- ПЛИС: XCKU040-2FFVA1156E

- Конфигурация:

- Через USB программатор на плате

- Через колодку для Platform Cable USB II (поставляется отдельно)

- Энергонезависимая память Quad SPI Flash with 2 x 256 Mb

- Память:

- 2GB DDR4 (четыре микросхемы [256 Mb x 16]) 1200MHz / 2400Mbpsps

- 64MB (512Mb) Quad SPI Flash

- 8Kb IIC EEPROM

- Micro SD Card Slot

- Коммуникационные и сетевые интерфейсы:

- Gigabit Ethernet GMII, RGMII и SGMII

- 2x SFP / SFP+

- GTX port (TX, RX) четыре SMA

- UART To USB Bridge

- PCI Express x8

- Отображение:

- Выход HDMI

- 8x GPIO user LEDs

- Порты расширения:

- FMC-HPC (8 GTX Transceiver, 114 single-ended or 57 differential (34 LA & 24 HA) user defined signals)

- FMC-LPC (1 GTX Transceiver, 68 single-ended or 34 differential user defined signals)

- 2x PMOD

- IIC

- Тактирование:

- Восемь программируемых тактовых сигналов

- Два входа для внешнего тактирования через SMA

- Управление:

- 5 кнопок

- 4X DIP переключателя

- 1x поворотный переключатель

- Диф пара через SMA

- Питание:

- 12V блок питания или через ATX

- ПЛИС: XCKU040-2FFVA1156E

Что включено:

-

-

- Плата KCU105

- Два модуля SFP+ производительностью 10Gbps

- Оптический кабель

- Лицензия Vivado® Design Suite: Design Edition (Device-locked to the XCKU040)

- Доступ к референс дизайнам

-

Описание на сайте производителя: http://www.xilinx.com/products/boards-and-kits/kcu105.html

Парт номер для заказа: EK-U1-KCU105-G

О платформе UltraScale

Новая платформа UltraScale – это в первую очередь переход на новый технологический процесс 20 нм, а в последствии 15 нм, позволяющий сократить потребление и увеличить производительность ваших устройств.

Обновленная архитектура нового семейства решает сразу несколько проблем:

- Доминирование задержки маршрутизации над общей задержкой в системе при росте объема кристалла

- Задержка такта в системе становится существенной из-за ограничений при масштабировании системы тактирования

- Неоптимальная упаковка логики снижает производительность

Добавление дополнительных слоев металлизации позволило увеличить число межсоединений, и находить кратчайший путь между элементами.

Отход от центральной схемы тактирования позволяет оптимально распределить такт по схеме.

Новая архитектура блоков CLB позволяет Vivado более компактно упаковывать дизайн

Применение аппаратных ядер 100G Ethernet, 150G Interlaken и PCIe Gen 3 вместе с новыми трансиверами стандарта GTY (32.75 GB/s) позволяют поднять максимальную скорость обмена ПЛИС с внешними устройствами.

Более подробную информацию по обновленной архитектуре можно посмотреть на сайте производителя: http://www.xilinx.com/support/documentation/white_papers/wp434-ultrascale-smarter-systems.pdf