# Расширяемая процессорная

# платформа семейства Zynq-7000

В марте 2011 года состоялся выход версии САПР ISE 13.1 фирмы Xilinx, мирового лидера в производстве ПЛИС с архитектурой FPGA. В серии анонсов новых продуктов, в частности, была опубликована информация о ПЛИС семейства Zyng-7000, открывающих новый класс микросхем Xilinx — FPGA с аппаратными ядрами процессора ARM. Заявленные характеристики этих микросхем и сочетание ресурсов требуют переосмысления подходов к проектированию процессорных систем на базе ПЛИС.

**Μπρα ΤΑΡΑΓΩ**

#### Введение

Новое семейство FPGA фирмы Xilinx было анонсировано одновременно с предоставлением доступа к САПР ISE версии 13.1, хотя его поддержка запланирована в последующих версиях САПР. Ввиду того, что в настоящее время ПЛИС с использованием технологических норм 28 нм не выпускаются и появления первых инженерных образцов следует ожидать не ранее 2012 года, предполагается ознакомление с предварительными характеристиками

Zynq-7000. Семейство позиционировано как новый подкласс FPGA — расширяемая процессорная платформа (Extensible Processor Platform, EPP). Основной особенностью этих ПЛИС является наличие на кристалле двухъядерного процессора ARM Cortex-A9, вокруг которого и предполагается построение системы. Наличие процессора с архитектурой, получившей широчайшее распространение в последнее время, позволяет разработчикам комбинировать методы проектирования из «обоих миров» — цифрового дизайна и программиро-

возможным комбинировать сильные стороны обоих подходов, сочетая программную реализацию широко распространенных алгоритмов и протоколов, имеющих поддержку в виде библиотек и средств разработки, и аппаратное ускорение несложных операций с высокой степенью параллелизма, выполняемое на базе программируемых ресурсов FPGA. Такой подход обеспечивает высокую гибкость в выборе методов и средств разработки, при этом основа — процессорное ядро — представляет собой мощное решение, поддерживаемое многими инструментами разработки и операционными системами.

вания встроенных систем. При этом становится

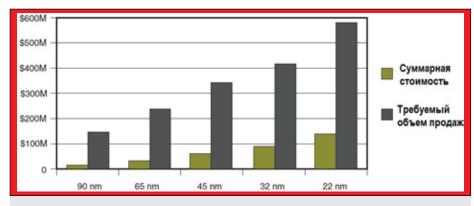

Регулярное возобновление интереса к встроенным системам на базе ПЛИС связано с постоянным повышением стоимости разработки заказных микросхем по мере уменьшения технологических норм. На рис. 1 показана зависимость суммарной стоимости разработки заказной микросхемы от нормы технологического процесса. На том же рисунке приведен требуемый для покрытия расходов на разработку объем продаж, в предположении, что из этой суммы должны быть скомпенсированы и расходы на производство, транспортировку, сопровождение, техническую поддержку и т.д.

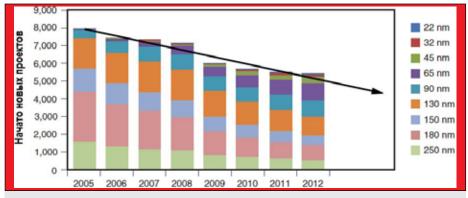

Анализируя рис. 1, видим, что производство новых микросхем становится оправданным только при реализации продуктов, выпускаемых массовым тиражом. Поэтому постоянно появляются рыночные ниши, для которых характерен небольшой тираж или регулярно меняющиеся технические требования, что снижает привлекательность разработки специализированных микросхем по сравнению с использованием FPGA. На рис. 2 показана существующая тенденция к уменьшению числа проектов по разработке новых заказных микросхем.

На рис. 2 также видно, что, несмотря на освоение новых технологических норм, в том числе 32 и даже 22 нм, количество продуктов,

Рис. 1. Зависимость суммарной стоимости разработки и требуемого объема продаж заказных микросхем от нормы технологического процесса

Рис. 2. Число новых проектов по разработке заказных микросхем в зависимости от года

Рис. 3. Классификация процессорных ядер ARM

проектируемых с применением этих норм, крайне мало. Свыше половины проектов базируются на процессах с нормами 130 нм и более, поскольку высокая стоимость производства с меньшими нормами заставляет производителей микросхем ориентироваться на более дешевые технологии. Исходя из этого, можно сделать вывод, что микросхемы, производимые с использованием современных технологических процессов, должны иметь настолько широкие возможности, чтобы обеспечить массовое применение, способное оправдать высокий уровень затрат на подготовку производства. Примерами такой широко распространенной продукции являются процессорные ядра ARM.

Процессорное ядро ARM Cortex-A9

Новые ПЛИС содержат сдвоенное ядро процессора ARM Cortex-A9 с памятью и набором периферии. Классификация процессорных ядер ARM приведена на рис. 3. На нем видно, что эти ядра отнесены разработчиком к одной из трех групп — Classic, Embedded и Application. При этом ядра группы Application можно встретить в таких устройствах, как мобильные телефоны, планшетные компьютеры, нетбуки, информационные системы и пр. Они способны обеспечить достаточно высокую производительность в задачах отображения информации, организации интерфейса с пользователем, поддержку разнообразных коммуникационных интерфейсов и устройств хранения данных. Немаловажным фактором является относительно низкое энергопотребление ядер ARM по сравнению с процессорами с архитектурой х86, также применяемыми в устройствах упомянутых типов. Размещение в ПЛИС двух ядер Cortex-A9 с тактовой частотой 800 МГц позволяет, таким образом, разрабатывать устройства с развитым пользовательским интерфейсом и разнообразными периферийными компонентами, пользуясь при этом средствами разработки, поддерживающими архитектуру ARM.

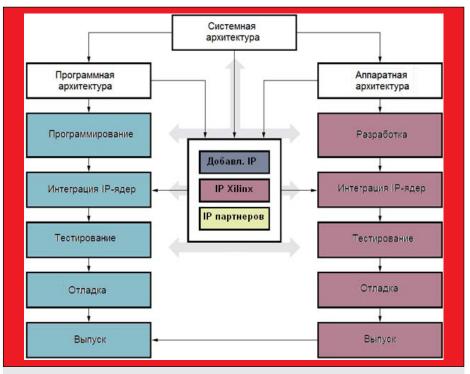

Наличие в той же микросхеме программируемых ресурсов требует скорректировать маршрут проектирования устройства, разделив его на проектирование программной и аппаратной составляющей, как это уже предлагалось для систем на базе софт-процессора MicroBlaze. В маршруте проектирования, показанном на рис. 4, представлено независимое протекание этих процессов, с добавлением к ним части работы системного архитектора. Действительно, проанализировав возможности программируемых ресурсов Zynq-7000, нетрудно пред-

ставить, что превращать такие микросхемы в еще одну разновидность микроконтроллера с ядром ARM попросту нецелесообразно. Видимо, неправильным было бы и полностью разделять работу ядер ARM и программируемой части микросхемы. Более рациональным решением представляется более или менее тесная интеграция стандартной, процессорной части кристалла и программируемой, выполняющей нестандартные операции путем загрузки соответствующей конфигурации, или массово-параллельные вычисления, ускоряющие работу ядер ARM. Поиск способов такой интеграции, идентификация задач для их аппаратного ускорения и является работой системного архитектора.

Характеристики ядра ARM в составе Zynq-7000:

- Ядро: сдвоенное Cortex-A9, тактовая частота 800 МГц.

- Расширения ядра: NEON, плавающая точка одинарной и двойной точности.

- Кэш первого уровня: 32 кбайт инструкций, 32 кбайт данных на каждое ядро.

- Кэш второго уровня: 512 кбайт.

- Накристальная память: 256 кбайт.

- Поддержка внешней памяти: DDR2, DDR3, LPDDR2.

- Каналов ПДП 8.

- Периферия:

- USB 2.0 (OTG) с ПДП 2;

- трехрежимный Etnernet с ПДП 2;

- SD/SDIO с ПДП 2;

- UART 2;

- CAN 2.0B 2;

- $I^{2}C 2;$

- SPI 2;

- GPIO 32 бита.

Рис. 4. Маршрут проектирования устройств на базе Zynq-7000

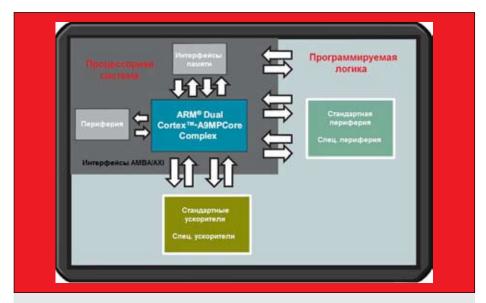

Рис. 5. Структура ядра ARM и его взаимодействие с периферийными устройствами и программируемыми ресурсами ПЛИС

**Таблица.** Состав семейства Zynq-7000

| плис                                                                           | Z-7010                                              | Z-7020     | Z-7030      | Z-7040      |

|--------------------------------------------------------------------------------|-----------------------------------------------------|------------|-------------|-------------|

| Программируемых логических ячеек (вентилей ASIC)                               | 28K (430K)                                          | 85K (1,3M) | 125K (1,9M) | 235K (3,5M) |

| Блоков памяти (по 36 кбайт)                                                    | 60                                                  | 140        | 265         | 760         |

| Секций DSP (18×25 MACC)                                                        | 80                                                  | 220        | 400         | 760         |

| Пиковая производительность DSP<br>для KИX с симметричными компонентами, GMAC/s | 58                                                  | 158        | 480         | 912         |

| Блоков PCI Express                                                             | -                                                   | -          | Gen2 ×4     | Gen2×8      |

| АЦП                                                                            | 2×12 бит, 1 Мвыборок/с, 17 дифференциальных каналов |            |             |             |

| Шифрование                                                                     | AES и SHA 256-бит                                   |            |             |             |

| Блоков ввода/вывода, 3,3В                                                      | 100                                                 | 195        | 100         | 200         |

| Блоков ввода/вывода, 1,8 B                                                     | _                                                   | -          | 150         | 150         |

| Высокоскоростных приемопередатчиков                                            | _                                                   | -          | 4           | 12          |

- Шифрование AES и SHA 256 бит.

- Мультиплексируемых линий памяти и ввода/вывода — 54.

- Интерфейсы к программируемым ресурсам:

- AXI 32 бита Master 2;

- AXI 32 бита Slave 2;

- AXI 64/32 бита, интерфейс с памятью 4;

- AXI 64 бита АСР;

- прерываний 16.

### Архитектура ПЛИС Zynq-7000 и состав семейства

Взаимодействие процессорных ядер ARM с программируемыми ресурсами схематично показано на рис. 5. На нем видно, что процессорный комплекс (понимая под этим термином оба ядра ARM с соответствующими шинами) взаимодействует с памятью и накристальной периферией без привлечения ресурсов программируемой логики, которая выступает в качестве аппаратной платформы для реализации дополнительных периферийных устройств и ускорителей вычислений, как стандартных, так и специальных, разрабатываемых для конкретного проекта. Представляется, что именно специально разрабатываемые ускорители и периферия могли бы стать теми компонентами, которые определят потребительскую привлекательность устройства, посколь-

ку устройства на базе ARM в настоящее время распространены весьма широко, и обеспечить конкурентное преимущество, концентрируясь на функциях, реализуемых программным обеспечением и периферией ARM, достаточно сложно. С другой стороны, реализовав параллельно работающую высокопроизводительную цифровую вычислительную систему на базе блоков цифровой обработки сигналов, можно использовать ARM в качестве аппаратной платформы для запуска пользовательского интерфейса, поддержки ОС (в числе которых можно упомянуть Linux и Windows CE), а также обработки аппаратных интерфейсов, реализация которых в ПЛИС потребовала бы привлечения дополнительных ресурсов -Ethernet, USB, CAN. Характеристики ПЛИС, которые в ближайшее время поступят в производство, представлены в таблице. Можно предполагать, что приведенные характеристики не являются окончательными, поскольку в настоящее время нет достоверной информации о начале производства и поставок как образцов, так и серийной продукции микросхем Zynq-7000.

Микросхемы Zynq-7010 и Zynq-7020 выполнены на базе программируемых ресурсов семейства Artix, а Zynq-7030 и Zynq-7040 на базе Kintex. Это отражается на пиковой производительности подсистемы цифровой обработки сигналов: в младших ПЛИС тактовая частота блока ниже. Также в младших ПЛИС нет блоков PCI Express и высокоскоростных приемопередатчиков.

### Примеры проектов на базе Zynq-7000, демонстрируемые Xilinx

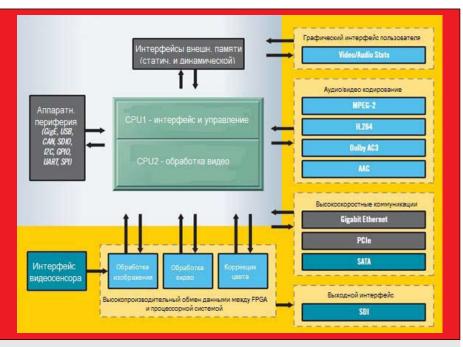

Для обработки видео в системах широковещательной передачи Zynq-7000 обеспечивают необходимую полосу пропускания данных. Использование процессорной системы (рис. 6) позволяет не только обеспе-

Рис. 6. Система широковещательной передачи данных с видеокамеры

Рис. 7. Система управления двигателем

чить выполнение всех требуемых операций, но и уменьшает потребляемую мощность и общую стоимость системы. Двухъядерного процессора ARM Cortex-A9 с расширениями NEON и плавающей точкой двойной точности достаточно для реализации алгоритмов кодирования видео в стандартах MPEG-2, H.264. Программируемая логика с большим количеством блоков DSP48 обеспечивает аппаратное ускорение часто используемых при кодировании видео операций, разгружая процессорную систему.

Следующая область применения Zynq-7000, демонстрируемая Xilinx, — это управление электроприводами (рис. 7). В данном случае конфигурируемые ресурсы FPGA позволяют реализовать модули, обеспечивающие реакцию на внешние события в реальном времени. Это важно для систем подобного класса, где с целью обеспечения надежности могут быть применены различные датчики, контролирующие достижение предельных для силовой части системы параметров — тока, температуры, координат, вращающего момента и т.п. Как правило, срабатывание таких датчиков должно приводить к мгновенной блокировке силовой части системы во избежание выхода из строя привода или силовых электронных компонентов. Конечно, такая блокировка может быть выполнена и управляющим процессором, однако следует обратить внимание, что по мере добавления функций в программное обеспечение потенциально могут возникать ситуации, когда процессор не сможет обработать запросы с датчиков системы защиты — например, если запрос приходит в момент, когда процессор обрабатывает прерывание с более высоким приоритетом. В этом

случае необходимо иметь уверенность, что программисты, работающие над программным обеспечением системы управления, понимают особенности функционирования таких устройств и при всех модификациях ПО учитывают необходимость обработки запросов от подсистемы аппаратной защиты.

В подобной ситуации существенно надежнее иметь модули, которые на аппаратном уровне обрабатывают запросы от датчиков, выполняя наиболее важные действия по бло-

кировке силовой части привода. В этом случае просчеты программистов в процессе отладки изделия не будут иметь такого разрушительного эффекта, а требования к надежности программного обеспечения существенно облегчаются.

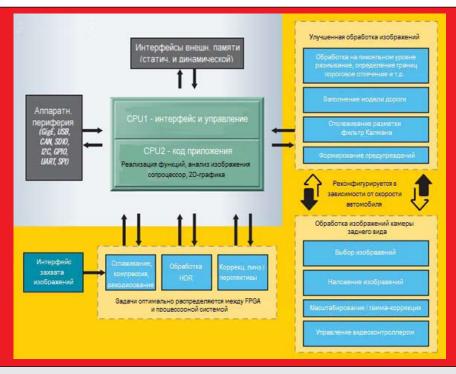

Наконец, последний из примеров относится к автомобильным системам. В данном случае рассматривается, например, driver assistant, «помощник водителя», обеспечивающий в основном анализ изображений (рис. 8) — отслеживание разметки, объектов, формирование для водителя изображения с камеры заднего вида и т. д. При этом используется смена конфигурации FPGA, когда при различных режимах движения загружаются аппаратные ускорители функций, требуемых в данное время. Такая возможность является ключевой для FPGA, что позволяет при минимальных аппаратных затратах обеспечить выполнение целого набора операций, необходимых в разных режимах.

В этой сфере полезным периферийным устройством является интерфейс CAN, наличие которого облегчает интеграцию Zynq-7000 в электронную систему автомобиля.

## Доступность и рекомендации

Сейчас сложилась неоднозначная ситуация, когда информация и инструменты проектирования для FPGA, выполненных по технологии с нормами 28 нм, существенно опережают сроки их возможного появления на рынке. Поэтому разработчики, планирующие использование этой элементной базы в своих проектах, находятся в сложном положении, испытывая определенное давление со стороны

Рис. 8. Система анализа изображений в автомобильном процессоре (driver assistant)

потенциальных заказчиков, имеющих информацию о характеристиках ПЛИС серии 7 фирмы Xilinx. Исходя из рекомендаций официальных дистрибьюторов, можно настоятельно рекомендовать не планировать использование FPGA Zynq-7000, а также остальных ПЛИС серии 7 (Artix, Kintex, Virtex-7) в проектах, завершающихся в 2012 году. Несмотря на то, что сроки начала поставок могут быть и пересмотрены, это не снижает степень риска, поскольку даже поставки образцов отдельных микросхем запланированы только на 2012 год. Поэтому в настоящий момент можно рассматривать семейства Virtex-6 и Spartan-6 в качестве основных, планируя освоение процессора ARM для будущего использования Zynq-7000. Можно также подчеркнуть, что архитектуры 6-й и 7-й серий FPGA Xilinx максимально приближены друг к другу, что позволяет уже сейчас моделировать решения, предназначенные для серии 7. При этом, однако, необходимо учитывать возможность изменения характеристик серийной продукции в процессе уточнения производителем ее характеристик.

Также можно обратить внимание на системы на базе софт-процессора MicroBlaze, освоение проектирования которых облегчит в дальнейшем переход к ARM вследствие схожести маршрута проектирования и используемых инструментов разработки.

#### Заключение

Новое семейство FPGA открывает принципиально новую линейку продуктов фирмы Xilinx. Ранее аппаратные процессорные ядра принадлежали к семейству PowerPC и размещались в FPGA верхнего ценового диапазона. Однако производительность как вычислений, так и передачи данных в таких ПЛИС определялась в малой степени возможностями PowerPC и в существенно большей — возможностями матрицы программируемых ресурсов. Семейство Zynq-7000 стоит значительно ближе к ПЛИС начального уровня (уже потому, что младшие устройства основаны на программируемых ресурсах семейства Artix-7), поэтому роль процессора

в них более заметна. В то же время мощные вычислительные возможности FPGA достаточно сильно отличают Zynq-7000 от микроконтроллеров с ядром ARM, что позволяет ориентироваться при разработке на аппаратные ускорители.

Сейчас можно использовать семейства Virtex-6 и Spartan-6, которые имеют ту же архитектуру программируемых ресурсов, что и ПЛИС серии 7. Поэтому аппаратные ускорители, разработанные для этих ПЛИС, можно будет перенести и в Zynq-7000. Поддержка Zynq-7000 в ISE 13.1 отсутствует и запланирована в последующих обновлениях САПР.

#### Литература

1. DeHaven K. Extensible Processing Platform Ideal Solution for a Wide Range of Embedded Systems. WP369 (v1.0) April 27, 2010 — http://www.xilinx. com/support/documentation/white\_papers/ wp369\_Extensible\_Processing\_Platform\_ Overview.pdf